# Amlware Hardware Technology Drivers of Ambient Intelligence

Edited by Satyen Mukherjee, Emile Aarts, Raf Roovers, Frans Widdershoven and

Martin Ouwerkerk

#### AmIware

# Philips Research

#### VOLUME 5

Editor-in-Chief

Dr. Frank Toolenaar

Philips Research Laboratories, Eindhoven, The Netherlands

#### SCOPE TO THE 'PHILIPS RESEARCH BOOK SERIES'

As one of the largest private sector research establishments in the world, Philips Research is shaping the future with technology inventions that meet peoples' needs and desires in the digital age. While the ultimate user benefits of these inventions end up on the high-street shelves, the often pioneering scientific and technological basis usually remains less visible.

This 'Philips Research Book Series' has been set up as a way for Philips researchers to contribute to the scientific community by publishing their comprehensive results and theories in book form.

Ad Huijser

# **AmIware**

# Hardware Technology Drivers of Ambient Intelligence

#### Edited by

#### Satyen Mukherjee

Philips Research North America, New York, USA

#### **Emile Aarts**

Philips Research Laboratories, Eindhoven, The Netherlands

## Raf Roovers

Philips Research Laboratories, Eindhoven, The Netherlands

#### Frans Widdershoven

Philips Research, Leuven, Belgium

and

#### Martin Ouwerkerk

Philips Research Laboratories, Eindhoven, The Netherlands

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-4197-7 (HB) ISBN-13 978-1-4020-4197-6 (HB) ISBN-10 1-4020-4198-5 (e-book) ISBN-13 978-1-4020-4198-3 (e-book)

> Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

> > www.springer.com

Printed on acid-free paper

All Rights Reserved © 2006 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

## **Contents**

| Contrib                   | uting Authors                                                | ix  |

|---------------------------|--------------------------------------------------------------|-----|

| Preface                   | - Satyen Mukherjee                                           | XV  |

| Acknowledgement – Editors |                                                              |     |

| Forewo                    | rd – Hugo De Man                                             | xxi |

| Section                   | 1. Introduction                                              | 1   |

| 1.1                       | Ambient Intelligence: The Next Wave in Consumer              |     |

|                           | Electronics                                                  | 3   |

|                           | Rick Harwig                                                  |     |

| 1.2                       | The Physical Basis of Ambient Intelligence                   | 9   |

|                           | Henk van Houten                                              |     |

| Section                   | 2. Wireless Communication                                    | 29  |

| 2.1                       | Circuits and Technologies for Wireless Sensor Networks       | 31  |

|                           | Brian Otis, Mike Sheets, Yuen-Hui Chee, Huifang              |     |

|                           | Qin, Nathan Pletcher, and Jan Rabaey                         |     |

| 2.2                       | Wireless Connectivity for In Home Audio/Video Networks       | 51  |

|                           | Gerhard Fettweis, Ralf Irmer, Marcus Windisch, Denis         |     |

|                           | Petrovic, and Peter Zillmann                                 |     |

| 2.3                       | <b>Body Area Networks: The Ascent of Autonomous Wireless</b> |     |

|                           | Microsystems                                                 | 73  |

|                           | Bert Gyselinckx, Chris Van Hoof, and Stephane Donnay         |     |

| 2.4                       | Wireless Communication Systems                               | 85  |

|                           | Neil C. Bird                                                 |     |

| Section                   | 3. Smart Sensors                                             | 105 |

| 3.1                       | Interconnect and Packaging Technologies for Realizing        |     |

|                           | Miniaturized Smart Devices                                   | 107 |

|                           | Eric Beyne                                                   |     |

vi Contents

| 3.2        | CMOS Image Sensors for Ambient Intelligence                                      | 125 |

|------------|----------------------------------------------------------------------------------|-----|

|            | Albert J.P. Theuwissen, Martijn F. Snoeij, X. Wang,                              |     |

|            | Padmakumar R. Rao, and Erik Bodegom                                              |     |

| 3.3        | Microsystem Technology for Ambient Intelligence                                  | 151 |

|            | Geert Langereis                                                                  |     |

| Section    | 4. Low Power Electronics and System Architecture                                 | 179 |

| 4.1        | Low Energy Digital Circuit Design                                                | 181 |

|            | Benton H. Calhoun, Curt Schurgers, Alice Wang,                                   |     |

|            | and Anantha Chandrakasan                                                         |     |

| 4.2        | Analog Interface Circuits—The Limit for AmI Applications                         | 203 |

|            | Michiel Steyaert, Willem Laflere and Wim Vereecken                               |     |

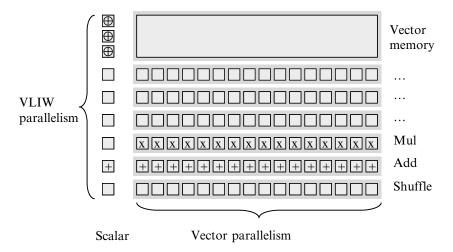

| 4.3        | Vector Processing as an Enabler for Ambient Intelligence                         | 223 |

|            | Kees van Berkel, Anteneh Abbo, Srinivasan Balakrishnan,                          |     |

|            | Richard Kleihorst, Patrick P.E. Meuwissen, Rick Nas                              |     |

| 4.4        | Xtreme Low Power Technlogy Development Using a Virtual                           |     |

|            | Design Flow: Enabling Technologies for Ambient                                   |     |

|            | Intelligence Applications                                                        | 245 |

|            | P. Christie, R. K. M. Ng, G. Doornbos, A. Heringa,                               |     |

|            | A. Kumar, and V. H. Nguyen.                                                      |     |

|            | 5. Energy Supply and Management                                                  | 263 |

| 5.1        | <b>Energy Scavenging in Support of Ambient Intelligence:</b>                     |     |

|            | Techniques, Challenges, and Future Directions                                    | 265 |

|            | Shad Roundy, V. Sundararajan, Jessy Baker, Eric Carleton,                        |     |

|            | Elizabeth Reilly, Brian Otis, Jan Rabaey, and Paul Wright                        | •   |

| 5.2        | Power Management Options for AmI Applications                                    | 285 |

| <b>5</b> 2 | Derk Reefman, and Eugenio Cantatore                                              |     |

| 5.3        | Rechageable Batteries: Efficient Energy Storage Devices for Wireless Electronics | 215 |

|            | P.H.L. Notten                                                                    | 315 |

|            | P.H.L. Notten                                                                    |     |

|            | 6. Enabling Technologies and Devices                                             | 347 |

| 6.1        | Personal Healthcare Devices                                                      | 349 |

|            | Steffen Leonhardt                                                                |     |

| 6.2        | Carbon Nanotube Field-effect Transistors—The Importance                          | 251 |

|            | of Being Small                                                                   | 371 |

|            | Joachim Knoch and Joerg Appenzeller                                              | 402 |

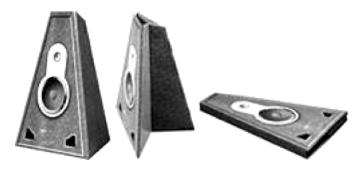

| 6.3        | Hardware for Ambient Sound Reproduction                                          | 403 |

|            | Ronald M. Aarts                                                                  |     |

| CONTENTS                                          | vii |

|---------------------------------------------------|-----|

| 6.4 Secret Key Generation from Classical Physics: |     |

| Physical Uncloneable Functions                    | 421 |

| Pim Tuyls and Boris Škorić                        |     |

| Section 7. Conclusions                            | 449 |

| 7.1 Conclusions and Key Challenges                | 451 |

| Satyen Mukherjee                                  |     |

| Subject Index                                     | 459 |

| Author Index                                      | 471 |

|                                                   |     |

#### **Contributing Authors**

#### Ronald M. Aarts

Philips Research Eindhoven ronald.m.aarts@philips.com

#### **Anteneh Abbo**

Philips Research Eindhoven anteneh.a.abbo@philips.com

#### Joerg Appenzeller

IBM Research joerga@us.ibm.com

#### Jessy Baker

University of California at Berkeley

#### Srinivasan Balakrishnan

Philips Research Eindhoven srinivasan.balakrishnan@philips.com

#### Kees van Berkel

Philips Research Eindhoven Eindhoven University of Technology kees.van.berkel@philips.com

#### **Eric Beyne**

IMEC, Leuven eric.beyne@imec.be

#### Neil C. Bird

Philips Research Eindhoven neil.bird@philips.com

#### Erik Bodegom

Department of Microelectronics/DIMES, Delft University of Technology bodegom@pdx.edu

#### Benton H. Calhoun

University of Virginia bcalhoun@virginia.edu

#### **Eugenio Cantatore**

Philips Research Eindhoven eugenio.cantatore@philips.com

#### **Eric Carleton**

University of California at Berkeley

#### **Anantha Chandrakasan**

Massachusetts Institute of Technology anantha@mtl.mit.edu

#### Yuen-Hui Chee

Berkeley Wireless Research Center, University of California, Berkeley

#### P. Christie

Philips Research Leuven p.christie@philips.com

#### **Stephane Donnay**

IMEC, Leuven

#### G. Doornbos

Philips Research Leuven gerben.doornbos@philips.com

#### **Gerhard Fettweis**

Technische Universität Dresden fettweis@ifn.et.tu-dresden.de

#### **Bert Gyselinckx**

IMEC, Leuven bert.gyselinckx@imec-nl.nl

#### Rick Harwig

Philips Research Eindhoven rick.harwig@philips.com

#### A. Heringa

Philips Research Leuven anco.heringa@philips.com

#### **Chris Van Hoof**

IMEC, Leuven

#### Henk van Houten

Philips Research Eindhoven henk.van.houten@philips.com

#### **Ralf Irmer**

Technische Universität Dresden irmer@ifn.et.tu-dresden.de

#### **Richard Kleihorst**

Philips Research Eindhoven richard.kleihorst@philips.com

#### Joachim Knoch

Institute for Thin Films and Interfaces, Forschungszentrum Jülich j.knoch@fz-juelich.de

#### A. Kumar

Philips Research Leuven aatish.kumar@philips.com

#### Willem Laflere

ESAT-MICAS, KULeuven willem.laflere@esat.kuleuven.be

#### **Geert Langereis**

Philips Research Eindhoven geert.langereis@philips.com

#### Steffen Leonhardt

Helmholtz Institute of Biomedical Engineering, RWTH Aachen University medit@hia.rwth-aachen.de

#### Hugo De Man

Katholieke Universiteit Leuven, IMEC deman@imec.be

#### Patrick P.E. Meuwissen

Philips Research Eindhoven patrick.meuwissen@philips.com

#### Satyen Mukherjee

Philips Research North America satyen.mukherjee@philips.com

#### Rick Nas

Philips Research Eindhoven rick.nas@philips.com

#### R.K.M. Ng

Philips Research Leuven ranick.ng@philips.com

#### V.H. Nguyen

Philips Research Leuven viet.nguyenhoang@philips.com

#### P.H.L. Notten

Philips Research Eindhoven, Eindhoven University of Technology peter.notten@philips.com

#### **Brian Otis**

Electrical Engineering Department, University of Washington, Seattle botis@ee.washington.edu

#### **Denis Petrovic**

Technische Universität Dresden petrovic@ifn.et.tu-dresden.de

#### **Nathan Pletcher**

Berkeley Wireless Research Center, University of California, Berkeley

#### **Huifang Qin**

Berkeley Wireless Research Center, University of California, Berkeley

#### Jan Rabaey

Berkeley Wireless Research Center, University of California, Berkeley jan@eecs.berkeley.edu

#### Padmakumar R. Rao

Department of Microelectronics/DIMES, Delft University of Technology p.rao@tudelft.nl

#### **Derk Reefman**

Philips Research, Eindhoven derk.reefman@philips.com

#### Elizabeth Reilly

University of California at Berkeley

#### **Shad Roundy**

LV Sensors sroundy@lvsensors.com

#### **Curt Schurgers**

University of California, San Diego curts@ece.ucsd.edu

#### **Mike Sheets**

Berkeley Wireless Research Center, University of California, Berkeley

#### Boris Škorić

Philips Research Eindhoven boris.skoric@philips.com

#### Martijn F. Snoeij

Department of Microelectronics/DIMES, Delft University of Technology m.f.snoeij@tudelft.nl

#### **Michiel Steyaert**

ESAT-MICAS, KULeuven michiel.steyaert@esat.kuleuven.be

#### V. Sundararajan

University of California at Riverside vsundar@engr.ucr.edu

#### Albert J.P. Theuwissen

Department of Microelectronics/DIMES, Delft University of Technology a.j.p.theuwissen@tudelft.nl

#### Pim Tuyls

Philips Research Eindhoven pim.tuyls@philips.com

#### Wim Vereecken

ESAT-MICAS, KULeuven wim.vereecken@esat.kuleuven.be

#### Alice Wang

Texas Instruments aliwang@ti.com

#### X. Wang

Department of Microelectronics/DIMES, Delft University of Technology x.wang@tudelft.nl

#### **Marcus Windisch**

Technische Universität Dresden windisch@ifn.et.tu-dresden.de

#### Paul Wright

University of California at Berkeley

#### Peter Zillmann

Technische Universität Dresden zillmann@ifn.et.tu-dresden.de

#### **Preface**

The term Ambient Intelligence (AmI) has come to symbolize systems, designed to serve us, that are embedded in our surroundings and are context aware, adaptive and anticipatory. Ambient Intelligence systems have been around for much longer than many of us would imagine. If we look at our surroundings—our homes, offices, automobiles or public places—we might realize that evolving technologies have been making us more comfortable, safe and content for some time. Fire or burglar alarm systems are examples of early AmI technologies. These early systems were followed by basic devices such as motion detectors coupled with lighting controls in homes and offices. Considered elementary today, these early applications are often not classified as AmI due to the limited intelligence involved in these systems.

Typically, the process of application innovation is driven by a two-pronged effort—the application pull from the top and technology capability push from the bottom. High performance and high functionality technologies trigger creative ideas leading to innovative applications. Or, creative minds conceive of new ideas and then seek practical technological solutions. In either approach, a close interaction between the two levels (top and bottom) is conducive to meaningful innovation.

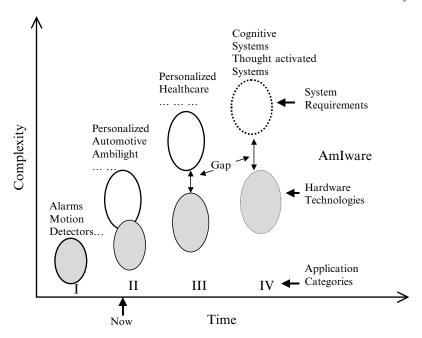

AmI applications can be classified into four broad categories based on the maturity level:

- I. Applications that already exist in the marketplace.

- II. Applications in the development phase that primarily involve technology integration. Here system requirements are well defined and practical integration is the major challenge.

- III. Applications requiring a basic technology breakthrough to accomplish the requirements. The requirements are mostly known but implementation technologies are not fully available.

- IV. Applications which are not completely defined but are more in the idea phase. These typically have to do with providing cognitive

xvi Preface

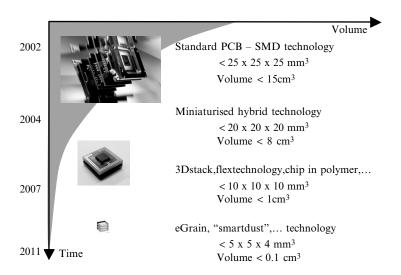

Figure 1. The AmI Application categories and the capability gap.

functionality and the like. The technology requirements are not clearly defined but expectations exist.

From a research perspective the last three categories are of interest. One can map ideas in the appropriate categories to determine requirements and challenges. The number order reflects the degree of challenge which consequently is related to the time frame for practical implementation as depicted in figure-1. Also depicted in the figure is the increasing gap between system level ideas and practical technology capabilities.

The process of top down innovation in AmI has been addressed in numerous conferences, seminars and publications in the past. To complement this effort, a symposium was held to emphasize the bottom-up process to help bridge the gap between the top-down thinkers and the bottom-up innovators. This book is based on the contributions to the symposium "Hardware Technology Drivers of Ambient Intelligence (AmI)", held on Dec 9-10, 2004 at The Koningshof, Veldhoven, the Netherlands. Technical experts from around the world were invited to present developments in various hardware technologies, relevant to AmI. Defining the term AmIware for these hardware technologies, the authors were asked to identify the drivers of their respective technologies with

PREFACE xvii

regard to AmI applications. Key hardware technologies were selected based on their relative importance in AmI applications.

The book begins with a broad overview of the physical layer of AmI applications and is followed by five sections covering key technologies that are relevant to AmI applications:

- Wireless communications

- Smart sensors

- Low power electronics

- Energy supply and management

- Enabling technologies and devices

Papers in each section cover different elements of hardware technologies, describe the state of the art and identify challenges that need to be addressed to bridge the capability gap shown in figure-1. A concluding chapter summarizes and adds to the key hardware challenges that need to be addressed in the future.

It is hoped that this bottom-up effort to identify some of the main hardware technologies (AmIware) and the challenges involved will inspire top-down thinkers to devise meaningful AmI applications and solutions. Bridging the existing gap between the system architects and the hardware technologists will allow us to create truly rewarding consumer applications that will improve our quality of life.

Satyen Mukherjee Philips Research

#### Acknowledgements

Aside from the contributing authors of the chapters we would like to thank the management of Philips Research for their inspiration and support in putting together this book. We would like to especially thank Audrey Tobin for her assistance in coordinating the editing process.

Satyen Mukherjee, Philips Research North America Emile Aarts, Philips Research Laboratories Eindhoven Raf Roovers, Philips Research Laboratories Eindhoven Frans Widdershoven, Philips Research Leuven Martin Ouwerkerk, Philips Research Laboratories Eindhoven

#### **Foreword**

Hugo De Man Professor Katholieke Universiteit Leuven Senior Research Fellow IMEC

Ambient intelligence (AmI) refers to the vision of a world in which secure, trustworthy computing and communication will be embedded in everything and every-body. This will create a pervasive, context aware electronics ambient that is adaptive and sensitive to the presence of people. It is all about cooperating electronic systems that will enrich human experience and improve the quality of life in an unobtrusive way.

So far much attention has been paid to application scenarios that often look like dreams in a far future. It is now time to pay attention to the realities of hardware technologies and engineering art needed to realize these dreams. This book is one of the first to fill the gap between scenario dreams and hardware reality. It is a compilation of contributions to an international workshop on state-of-the-art hardware suited for ambient intelligent systems organized by Philips NV in December 2004.

Ambient intelligent systems are very heterogeneous in nature and require the smooth cooperation between a wide variety of hardware technologies. Design of such systems is interdisciplinary by nature and requires an intense dialog between specialists of multiple domains. This book reports on the dialog between such specialists working on hardware issues that fit within the framework of AmI systems.

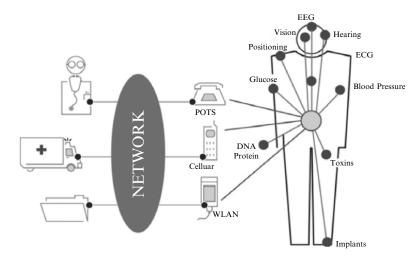

Personal healthcare and wellness, smart home systems and the progress of communication networks are taken as the system drivers in this book.

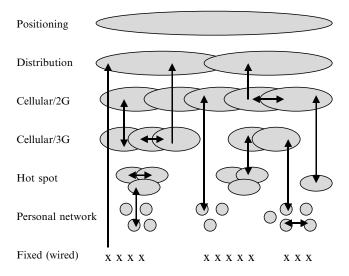

These driving applications define the AmI framework, which consists of tether less networking between people and objects, of transducer networks to sense and actuate the ambient and the human body, of interfacing to the human senses, and of wearable or stationary embedded computing to provide intelligence, interpretation and smart interaction when necessary.

xxii Foreword

Pervasive to all of the above is the extreme requirement on the energy efficiency of all hardware components either because they are nomadic (small size battery or fuel cell powered) or because they are cheap such that cooling cost and packaging must be minimized or, last but not least, because sensors and actuators must be autonomous also from an energy standpoint. This leads to the concept that they must scavenge their energy from the ambient itself. All of this introduces great challenges that cover a wide spectrum of hardware technologies.

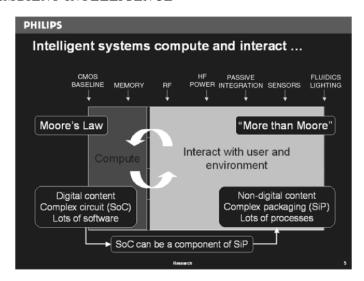

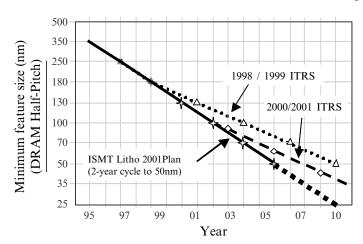

Wearable computing and communication systems operating on huge databases of audiovisual data will require "More Moore" i.e. further relentless scaling of digital devices down to the nano-scale dimensions to provide the giga-scale complexity required by AmI computing and datastorage within the energy constraints discussed above, while keeping embedded software programmability to provide flexibility and adaptivity. As all AmI systems have to communicate with the analog nature of human interfaces particular challenges occur to analog electronics in a nano-scaled device world. These "More Moore" issues are covered in the section on Low Power Anaolog and Digital Electronics and Technology.

Next to the above world of "More Moore" there is the world of "More than Moore". This refers to the plethora of hardware technologies on top of CMOS that are needed for interfacing to the real world and to the human body and senses. Sensors are a crucial part of all AmI systems leading to exciting requirements on MEMS, on cheap but ever more powerful optical sensors as well as on biosensors to couple bionics to electronics while no sensor is complete without appropriate packaging technology. These issues are covered in the section on Smart Sensors. But AmI is also about providing experience to people and hence actuators must provide natural light, sound and image experience to people. The section on Actuation provides us with state-of-the art realizations in solid-state lighting, flexible displays and the latest in high quality sound reproduction within an extremely small form factor.

Last but not least, the section on power supply and energy scavenging pays attention to one of the key technologies of nomadic devices and transducer nodes: power supply and power management. Opportunities and limitations on energy scavenging are reported and recent progress in flexible batteries with highly improved efficiencies are reported. This book is one of the first to bring all these hardware aspects together under one cover. It is recommended to all engineers involved in the realization of the AmI dream and is an inspiring source to create a dialog between the many hardware disciplines that must become interoperable to create a working AmI system. It is precisely that global system aspect that makes AmI such

FOREWORD xxiii

an exciting discipline that promises to have a great impact on society and on economical progress.

Leuven, March 2005

# Section 1

Introduction

# AMBIENT INTELLIGENCE: THE NEXT WAVE IN CONSUMER ELECTRONICS

Rick Harwig Philips Research Eindhoven rick.harwig@philips.com

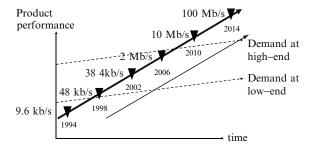

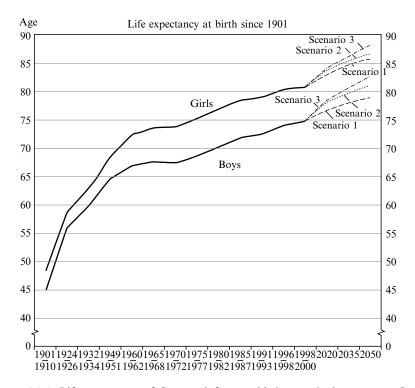

The history of consumer electronics has been marked by major advances in each of the past three decades, the 1970s, 1980s, and 1990s. Our present era (2000–2010) holds the promise of even more exciting technological progress. The seventies (1970–1980) could be called the era of the "hardware wave" when major consumer electronic (CE) devices, such as TVs and VCRs, were primarily hardware-based and product differentiation came from component technologies and system architectures. As component technologies matured and became commoditized, software became the key factor in product innovation, contributing to differentiation in device applications such as the CD player and the PC. Thus, 1980-1990 could be called the "software decade." With the nineties (1990-2000) came the "network wave" when markets became flooded with devices such as the mobile phone. The Internet took off in a major way and the world became increasingly more connected through all kinds of information systems. The networks and their performance were the differentiators. The present era (2000–2010) belongs to a new class of technologies called ambient intelligence (AmI). AmI, along with commodity hardware, standardized software, and networks that are becoming ubiquitous, is transforming the way that we utilize and experience traditional products and services. AmI will manifest itself in many ways and affect our lifestyle in a fundamental manner. Characterized by invisible electronics embedded in our environment (ambient) the AmI system will be capable of automatically responding to our needs and even desires (intelligence). This vision has been embraced by the European Union with a 3.6 billion Euro ICT program until 2006.

The need for AmI can be traced back to the dark ages when people were at the mercy of nature with little control over their environment. Improvements came gradually until the era of broadcast radio and television which represented a major leap toward allowing ready access to information. Today with mobile phones and the internet, information access is unrestricted in space and time. In the coming era AmI will bring us a step further in enhancing our lives and simplifying control of our environment.

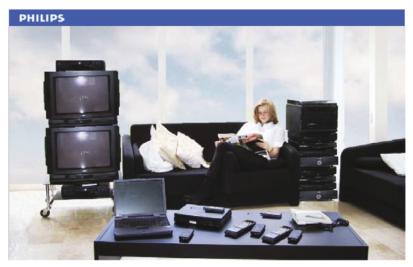

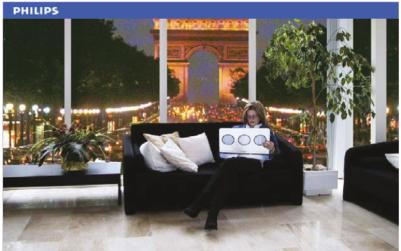

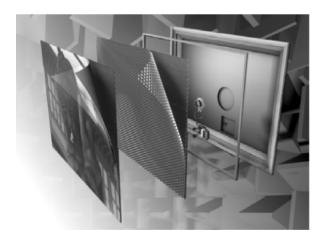

From the consumer electronics point of view the most striking change in the living room between the last century and the next will be the disappearance of the entertainment boxes (TV, VCR, DVD player, and PC) and the appearance of an ambience (characterized by unobtrusive displays and sound reproduction systems) that surrounds the user in a simple manner but makes a profound difference in the user's overall living experience (Figure 1.1–1).

Philips has been engaged in the revolutionizing technology of AmI for some years now and has introduced a number of products to the market. The ambilight TV, for example, automatically adjusts the ambient light around a TV to extend the image viewing experience beyond the boundaries of the physical display as shown in Figure 1.1–2.

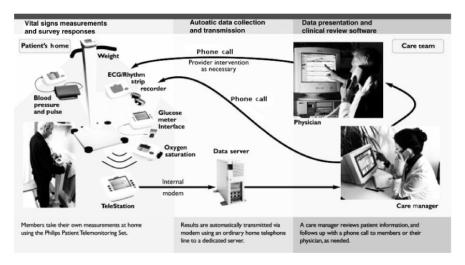

Electronic paper is another example of AmI where information is made conveniently available everywhere in a flexible manner. In the healthcare domain an example of particular interest to the physician is the 3D image rendering of vital organs, such as the human heart in real time as shown in Figure 1.1–3.

There are a number of key hardware technologies in the semiconductor arena that contribute to AmI applications. Important among them is the systems-in-package (SiP) that allows multiple functions to be integrated in one component module for a variety of applications. The celebrated Moores's law has allowed increasing functionality in system-on-chip (SoC) using digital CMOS technologies and primarily addressing computation applications. With the addition of components such as RF circuits, high voltage circuits, different types of sensors and even microfluidics and solid state light sources in the same SiP, implementation of AmI systems is moving closer to reality. The range of technologies and devices that can be integrated in a SiP are shown in Figure 1.1–4.

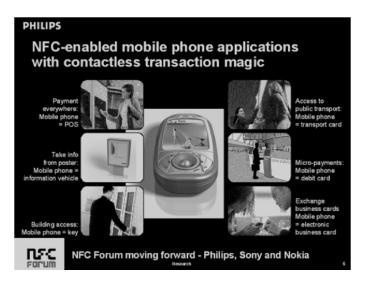

The near field communication (NFC)-enabled mobile phone is one of the recent applications introduced by Philips for a broad range of uses including mobile banking, money transactions, building access, public transport access, information display anywhere on the move, micropayment, and e-business cards as shown in Figure 1.1–5. This product involves a concerted effort between Philips, Sony, and Nokia.

Figure 1.1–1. The change in the living room from the last century (above) to the next (below) enabled by ambient intelligence (AmI).

AmI now represents embedded systems that are context aware, personalized, adaptive, and anticipatory to our needs and desires. Several institutions and companies around the globe are engaged today in various aspects of this exciting development, and a technology ecosystem is developing to address this field. Hardware advances continue to be one of the major drivers towards commercialization.

Figure 1.1–2. Philips ambilight TV.

Figure 1.1-3. 3D image rendering (of the human heart) for professional and consumer applications.

Figure 1.1-4. The domains of SoC and SiP.

Figure 1.1-5. NFC-enabled mobile phone and various application opportunities.

# THE PHYSICAL BASIS OF AMBIENT INTELLIGENCE

Henk van Houten

Philips Research Eindhoven

henk.van.houten@philips.com

Abstract Ambient intelligence (AmI) refers to future digital environments that are sensitive and responsive to the presence of people. This chapter addresses some challenges at the device level that need to be overcome to be able to realize a physical layer for AmI. As we will show, the physical layer of AmI cannot be realized by Moore's law type of innovation alone. The nontraditional functionality and form factors of the required devices call for heterogeneous integration and miniaturization approaches. The key enabling technologies are system-in-package(SiP) and large-area electronics. The soaring complexity of innovation in this field calls for open innovation approaches.

**Keywords** ambient intelligence; autonomous microdevices; displays; large area electronics; open innovation; sensors and actuators; solid state lighting; system-in-package

#### 1. INTRODUCTION

Ambient intelligence (AmI) refers to future digital environments that are sensitive and responsive to people [1]. We note that many other companies and institutes are studying concepts similar in spirit to AmI [2]. The concept of AmI has been studied primarily from a systems perspective, combining visionary insights from social science and computer science, and stressing the new experiences that will be enabled by future technologies. The AmI vision can be applied to very diverse application environments, varying from homes, offices, or cars to homes for the elderly and hospitals. It refers to all human senses: sight, hearing, touch, smell, and perhaps even taste. It also refers to a wide range of human

emotional and intellectual needs, from comfort, pleasure, and entertainment to safety, security, and health. In this chapter, we present an overview of the challenges that this vision poses to innovation in the field of devices and microsystems, which constitute the building blocks for the physical layer of AmI.

As we will discuss, the physical layer of AmI cannot be realized by Moore's law type of innovation alone. Next to mainstream system-on-chip (SoC) solutions for signal processing, solid state storage, and control, we expect that the nontraditional functionality and form factors of the required devices for ambient intelligent environments will require heterogeneous integration and a variety of miniaturization technologies. This inspires new paradigms in microelectronics, such as system-in-package (SiP) solutions, large area electronics, and textile electronics.

The SiP concept applies to quite diverse technology and application areas, ranging from sensors and actuators, RF modules for mobile communication devices, solid state lighting to health care devices, such as biosensors or cardiac pacemakers. The challenges include miniaturization and special packaging, allowing for a variety of input—output functionalities. Autonomous wireless sensor nodes, accepted to be essential components of ambient intelligent environments, pose the additional challenge of operation without having to replace batteries regularly, which requires ultra low power operation, and energy scavenging techniques.

Large area electronics has been developed in particular with active matrix displays as application carrier, and with amorphous or polycrystalline silicon on glass as the technology of choice. Polymer electronics is an emerging technology, which will allow large area flexible devices to be manufactured on plastic substrates, eventually using roll-to-roll technology. In addition to flexible displays, applications may include low cost RF tags, solar cells, or electronics embedded in paper. Light emitting polymers are being explored for display applications, but increasingly also as large area light sources. We predict that a cross fertilization will occur between the display and the lighting application domains, leading to new products such as pixel lamps. These can be used to generate special lighting effects, and novel user interfaces.

Finally, it will be a characteristic of ambient intelligent environments where electronics will be integrated in almost everything, including soft or deformable objects, such as furniture, curtains, or clothing. This field is known as textile electronics, which can be approached in quite different ways. One approach is to make functional fibers, which are subsequently woven into a fabric. Another is to integrate discrete electronic building blocks (made by SoC, SiP, or large area electronics technologies) into textile fabrics.

In the following sections, the physical layer of AmI is discussed while focusing on examples and concluding with remarks on the necessity of open innovation approaches in order to manage the soaring complexity associated with this field.

#### 2. THE ROOTS OF AMBIENT INTELLIGENCE

The concept of AmI builds upon the pioneering work by Mark Weiser on ubiquitous computing. A computer has already progressed enormously from the 1970's powerful mainframe, enshrined in a dedicated computing building, to the present day's almost equally powerful personal desktop computers and portable notebooks. The usage paradigm has remained essentially the same: input of data through typing on a keyboard, and output of data through a display. Weiser's vision was to make computers effectively *invisible* to the user, by having them distributed throughout the physical environment [3]. The display remains as the device to interact with.

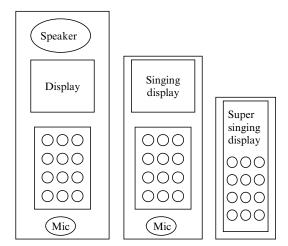

Weiser describes three such devices, ranging from a wall-sized interactive *board* (like an office whiteboard), a much smaller note *pad*, and really small devices called *tabs*. The tabs are of the size of the text on the spine of a book, or a post-it note. In a typical environment, the user would interact with one or two boards, tens of pads, and a swarm of tabs.

The essential point is that these computing devices should be unobtrusive: their size is determined by the display, and the rest is invisible. Many more unobtrusive devices are conceivable that do not have a display, for example sensor and actuators. These can be even smaller, leading to the concept of "smart dust" [4].

A second major pillar behind the concept of AmI is the work on intelligent social user interfaces by Nass and Reeves [5]. They wrote an influential book "The Media Equation", subtitled "How people treat computers, television, and new media like real people and places". Nass and Reeves found that human attributes like emotion, and aspects of human behavior like politeness, equally apply to the interaction of man with modern machines. Designing an effective user interface calls for an understanding of such psychological phenomena.

#### 3. THE VISION OF AMBIENT INTELLIGENCE

Philips has defined AmI as *digital environments that are sensitive and responsive to the presence of people*. It is not a purely technical vision but a people oriented vision. The emotional dimension is crucial. In this sense it

can be seen as a marriage of the unobtrusive computing world of Mark Weiser, and the sociological vision of human-media interaction of Nass and Reeves.

Putting emphasis on the emotional aspects is fully in line with an understanding of how the economic added value progresses through the stages of extracting commodity goods or materials (such as silicon or glass) to producing finished products out of the basic materials (such as an IC or a compact disc player) to delivering content or services (like music on a CD or broadcasting a movie) to staging experiences (like attending a live opera at La Scala in Milan). Putting it in a different way—people are prepared to pay substantially more for a cup of coffee at the Champs Elysées in Paris than at the office coffee machine. This is why in commercials a photo camera is not presented as a box one can shoot pictures with but as a tool to capture valuable or dear memories.

In a world where computing devices are "invisible," because they disappear into the background, it becomes even more important for companies to find innovative ways to capture the value. This must be done through selling experiences rather than products.

This vision requires electronic functions that are seamlessly integrated with the home, car, or office environment. These functions will be integrated in lifestyle products. Appliances will be smart, forming self-configuring networks. Wearable electronics, artificial intelligence, and sophisticated user interface functionality will be required.

Studies of human behavior will have to reveal whether people actually like to give orders to a picture on the wall, whether they would like to have their friends being "telepresent" while they are watching a soccer game in the living room. Will people appreciate having a wearable personal assistant that continuously monitors a number of biological functions, such as blood pressure or heart rate variability? Will they want the music and lighting atmosphere in their living room to adapt automatically to their unarticulated preferences? Philips Research has recently opened a "Home Lab" where such questions are being addressed by interdisciplinary teams through carefully designed and monitored experiments.

What does it take for an environment to be truly "ambient intelligent"? A key requirement is that many invisible or unobtrusive devices should be distributed throughout the environment. These should be *context aware*, in that they should know about their situational state. These devices should also be *personalized*, so that their function is tailored towards a specific user's needs. They should be *adaptive*, able to learn and recognize people. Ultimately, they should be *anticipatory*, wherein the user's desires are anticipated without the need for input by commands.

The scientific community tends to address these requirements from the perspective of the higher architectural layers of the system. Indeed, here one may find many interesting computer science challenges, such as data and content management, and dealing with data stored onto many different storage devices incorporated into a network. There is a strong link with connectivity problems, such as pervasive wireless networks, ubiquitous communication, or peer-to-peer computing. At a more subtle level, issues such as trust and privacy are very important, with associated disciplines, such as digital rights management, encryption, and biometric identification. User interface technologies, such as speech recognition and synthesis, or computer vision will be highly relevant as well. The ultimate system level challenge will be to design algorithms and programs for computational intelligence and contextual awareness.

#### 4. PHYSICAL LAYER CHALLENGES

Much less attention has been devoted so far to the physical layer of AmI, probably because of the implicit assumption that the Moore's law type of progress will provide all the technology that will be required. Weiser has mentioned some generic hardware issues: ultra low power computing, low-power small range communication (tiny cellular systems, with cells measuring just a cubic meter), and the realization of interaction devices, such as special pens for his digital whiteboards.

However, as discussed in this chapter, the physical layer of AmI is much richer than this. For example, we will need flexible displays that can be integrated into a variety of objects. We will have to invent soft controls and wearable displays for user interfaces integrated into garments or furniture. Smart RF identification tags, able to measure a variety of environmental parameters, will have to be incorporated into objects. A range of sensor and actuator functions will be required, with CMOS-enabled intelligence, integrated in miniature packages. These will also have to have a wireless communication function. And ideally, they would need to "scavenge" their energy from wherever and what is available in their environment. In the following paragraphs, a number of such physical layer challenges are discussed, without any claim to completeness.

#### 4.1. Displays Everywhere

In an ambient intelligent world, displays will be virtually everywhere. First of all, we will need large flat screens integrated in the walls of our living rooms or on our desks. For this purpose, liquid crystal displays with thin film

transistors are the current winning technology. LCD panel sizes are increasing steadily, and costs are coming down. Many of the performance issues, such as a limited viewing angle have been resolved. LCD panels are rapidly penetrating in the monitor market, and LCD-TV will be the next wave.

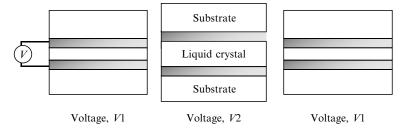

Manufacturing larger and larger LCD panels is requiring huge capital investments. It is intriguing to think about new ways to manufacture LCD panels, with the aim of achieving a cost breakthrough. For example, one may think of printing technologies to define the active matrix. It has been demonstrated by Philips Research that displays can be made using a bottom-up technology. Starting with a single substrate containing a pattern of interdigitated electrodes, this so-called stratified LCD technology [6] allows the formation of LCD cells using photoinduced phase separation and polymerization. Such a technology would eliminate one of the very large glass plates, and the associated complex handling issues.

LCD technology will clearly be an enabler for the realization of the vision of ubiquitous displays. A recent example is the so-called "Mirror TV" launched in 2003 by Philips. By integrating an LCD display behind a semitransparent mirror, display functionality is added to the bathroom mirror. This enables entirely new ambient intelligent applications.

LCD panels have various limitations as well. For example, they require a backlight. An emerging emissive display technology that does not require a backlight and offers very high quality color images, are active matrix panels with light emitting organic materials. There are currently two routes being pursued: conjugated polymers and oligomers. The small molecules require deposition by evaporation in vacuum, which is a relatively expensive method. The polymers are soluble and can be processed

Figure 1.2–1. A rollable display using a polymer electronics active matrix.

by spin coating or ink-jet printing. Full color inkjet-printed polymer-matrix displays suitable for high quality television applications have been shown to be possible. With emissive polymers, new types of displays can be made in principle, such as dual sided displays, or a transparent display integrated onto a window's pane.

Eventually, one would like to develop a reflective display technology that would offer high contrast images even under conditions of bright sunlight. Both LCD and polymer LED displays suffer from poor daylight contrast. A contender in the race towards developing real "electronic paper" is the electrophoretic display technology that is being developed jointly by e-ink and Philips. The principle is based on electrophoretic separation of white and black particles that are suspended in a liquid cell. It has now been demonstrated that gray scales are possible using sophisticated electrical switching strategies. The realization of full color electronic paper remains a challenge. A recent contender in this race is the electrowetting display, invented at Philips Research Laboratories [7].

One would like to have flexible displays as well, ranging from weakly curved displays that can be made conformal to the shape of an object or that can be integrated onto non-flat surfaces, such as car dashboards to displays that can be rolled up into a cylindrical container to paper like displays. Flexible displays are being investigated based on many of the known flat display principles. The manufacturing of the active matrix is one of the real challenges. LCD and e-ink panels can be switched with relatively low currents, and can probably be based on an amorphous silicon active matrix on flexible substrates. Organic LED displays demand larger driving currents, and will probably require a polycrystalline silicon active matrix. Polymer electronics is also a candidate technology for driving flexible displays. A desired breakthrough would be the invention of semiconducting organic materials with a much higher mobility than the conjugated polymers used so far. This would enable the realization of a fully organic display technology optimal for flexible displays. However, already today it is possible to make reflective flexible displays based on an electrophoretic display principle, in combination with a polymer electronics backplane (see Figure 1.2–1, courtesy of Polymer Vision).

#### 4.2 Sensing and Control

AmI calls for a multitude of different sensors to be embedded in the environment and into objects. As stated by Estrin et al, "interfacing to the physical world is arguably the single most important challenge in computer science today" [8].

The main physical layer challenges in this domain are integration and miniaturization, and function extension beyond measuring simple parameters, such as temperature, or pressure.

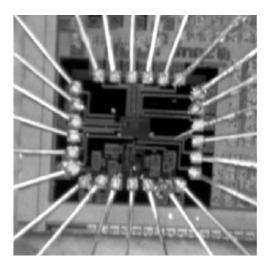

For known sensor principles, integration and miniaturization are the key challenge. This is needed, because it will be necessary to have very low cost sensors that can be unobtrusively integrated into objects. They will need to be integrated with a certain amount of silicon electronics, for preprocessing the data, for identification purposes, and for adding communication functionality. Microsystems and SiP technology are rapidly emerging as enablers for miniaturization of functions that cannot be realized using mainstream SoC technology. Whereas most analog and digital signal processing functions can now be integrated in standard IC processes, this is not true for many sensor and actuator functions or for discrete components, such as inductors, transformers, capacitors, and antennas, which require specific physical materials properties for their proper functioning.

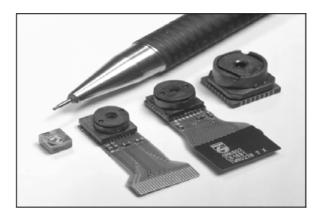

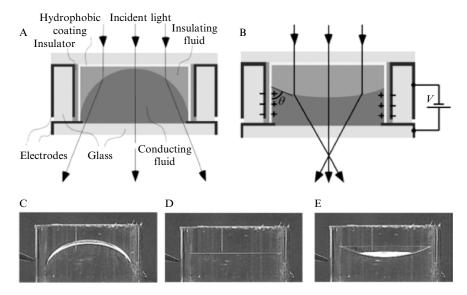

A wide range of physical parameters is easily accessible to measurement, such as temperature or heat flow. The orientation and acceleration of objects can be measured. Image capture is becoming a standard feature on mobile phones. Miniaturization of mechanical functions, such as zooming and focusing, will call for new types of adaptive optics. Philips has invented a miniature camera, comprising a CMOS image sensor and a tunable lens based on electrowetting (called Fluid Focus). Figure 1.2–2 illustrates various prototypes of this lens, showing the progression from a research demonstrator to a solution that lends itself to mass manufacturing. The phenomenon exploited in electro wetting lenses is the electric field dependence of the contact angle of a liquid at the walls of a container [9].

Figure 1.2-2. Successive prototypes of the Fluid Focus lens.

A rugged lens is made by adding a layer of oil on top of a layer of water. The two liquids have a different refractive index, but the same specific density, so that there are no undesired side effects of gravity or acceleration.

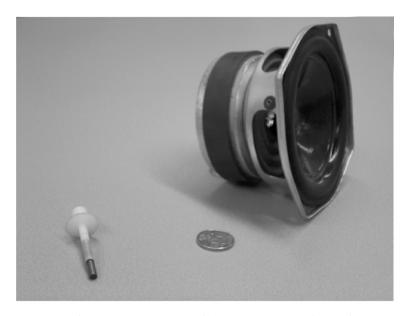

Also in the domain of function extension, microsystems technologies are very promising. For example, acoustic MEMS microphones and loud-speaker arrays in combination with phased-array technology and dedicated signal processing will enable miniature adaptive highly directional acoustic systems with obvious advantages for the suppression of background noise in mobile phones for speech recognition applications, and for directed speech output.

The chemical composition of the air in a room will give useful information that can be fed into air purification systems or in security systems (think of the Anthrax scare). Analysis of breath can provide information with a high clinical relevance (for example for patients suffering from asthma). But one can also think of sports coach systems requiring information on the lactate concentration in sweat. These applications will need chemical sensors, or biosensors. Such sensors can be made using a variety of different microsystems technologies, enhanced by surface modification with suitable capture molecules. MEMS like technologies can be added to manipulate gases or liquids.

The multitude of sensors embedded in ambient intelligent environments will have to communicate wirelessly to control systems, and possibly to each other. This calls for low power short-range communication systems, with appropriately designed miniature antennas.

#### 4.3 Autonomous Devices

The ultimate challenge in the field of AmI is to invent technologies for smart and *autonomous* microsystems. Such microsystems would typically need to incorporate sensor and communication functions. For applications where many autonomous devices are distributed throughout the environment, it would clearly be impractical to replace batteries all the time. Autonomous devices would therefore preferably be batteryless, taking their energy from the environment (visible or RF radiation, thermal gradients, vibration ... etc.). This is called energy scavenging.

An attractive practical example of an autonomous microdevice is the wireless wall switch marketed by EnOcean [10]. This "push button" generates 50  $\mu J$  of electrical energy by converting the mechanical energy associated with pushing the button on the switch, using a piezoelectric transducer. This is enough to meet the power demands of the electronic circuitry needed to transmit a payload of 250 bits using an RF

link at a bit rate of 100 kbit/s, at an activation lifespan of 2.5 ms (20 mW average power)

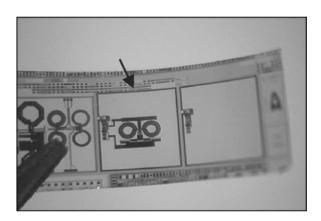

Familiar devices that can operate without a battery are the RF identification tags, that are rapidly becoming ubiquitous. These are *passive* devices, wherein the energy is provided from an external RF field generated by the reader device. Such RF devices enable intuitive interaction between devices and users through near field communication. Figure 1.2–3 shows a recently developed paper-thin RF tag made using "Silicon on Anything". In fact, this tag is so thin that it can be integrated into value paper.

Other wireless autonomous microsystems that are on the market today are tire pressure sensors. A practical example of an *active* autonomous microsystem is the quartz wristwatch powered by the irregular motion of the wrist. Also motion powered pace makers have been developed based on similar principles.

Various research laboratories have begun to study the design and system requirements for networks of smart and autonomous microdevices that operate in a collective fashion. The realization of such electronic dust [4] will be essential to make the vision of AmI come true. So far, most groups have focused on system design issues. Prototypes have been based on off-the-shelf components with a limited level of integration. Typically, a standard battery is used to power these early prototypes, and the battery tends to determine the size of the system.

We expect that (wireless) energy supply will remain the key limiting factor in the realization of ambient intelligent environments. Although there are some interesting approaches to integrated microbatteries and

Figure 1.2–3. Paper-thin RF powered tag made using the "Silicon on Anything" technology.

super capacitors, it is fair to say that progress in the energy storage density of batteries is by far not as impressive as that of the digital technologies mentioned above [11].

The amount of power that can be scavenged from the environment is a function of system size and of the strength of the driving forces. Rabaey has provided some estimates of attainable power levels [12] (Table 1.2–1):

From these numbers we can conclude that energy scavenging can provide typically  $10\text{--}1000\,\mu\text{W/cm}^2$  for a device of cm dimensions under normal conditions. It is of interest to contrast this to a typical battery, with an energy density of 400 Wh/l. Assuming continuous operation during 10 years without any recharging, such a battery can provide a power of  $4\,\mu\text{W/cm}^3$ . Of course, this number would rapidly go up in case recharging is allowed or if the operational lifetime could be shorter. For ambient intelligent environments with swarms of smart sensors it will clearly be impractical to exchange or recharge batteries.

Metrics from the field of IC design can be used to estimate what can be done with limited power. We should consider both computation and communication [13]. From the computational point of view, a power range of  $10\text{--}1000\,\mu\text{W}/\text{cm}^2$  would enable  $1\text{--}100\,\text{k}$  operations per second for the  $0.18\,\mu\text{m}$  CMOS technology node, neglecting leakage power. This would be just enough for low data rate sensor applications. Moore's law type technology scaling would enable successively more complicated computing applications, such as audio processing. Unfortunately, devices optimized for high performance computing have a rather large leakage power, typically  $0.01\,\mu\text{W}$  per device. For low complexity sensor applications, with 10000 devices, leakage power alone would already take as much as  $100\,\mu\text{W}$ , and this problem gets worse with scaling.

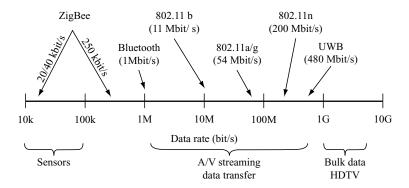

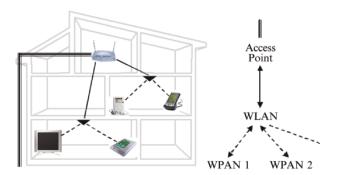

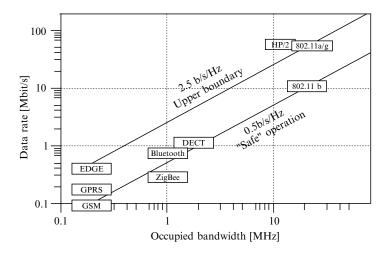

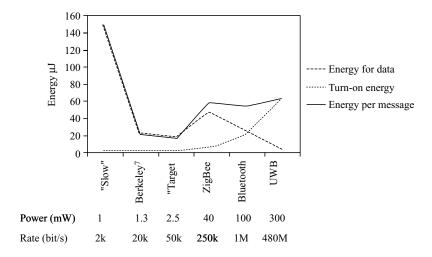

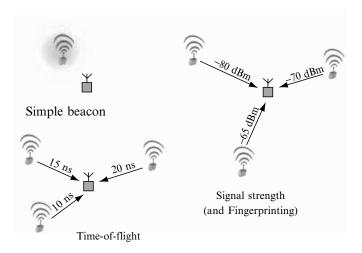

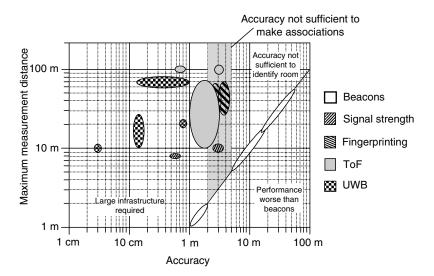

From the communications point of view, we should focus on the short range (on the order of meters). This is the realm of systems such as Bluetooth (1 Mbit/s), Zigbee (80 kbit/s), or PicoRadio (1 kbit/s). From these, only PicoRadio falls in the power consumption range of  $10-1000 \,\mu\text{W/cm}^2$ . Typically, the energy required to transmit a single bit over short ranges is in the order of  $10-30 \, \text{nJ}$ . This energy does not scale

Table 1.2-1. Energy scavenging [12].

| Energy source                         | Power density                 |

|---------------------------------------|-------------------------------|

| Vibrations                            | $0.05 - 0.5 \mathrm{mW/cm^3}$ |

| Sound pressure (100 dB)               | $1 \mu\mathrm{W/cm}^2$        |

| Temperature gradient (thermoelectric) | $1-10 \mu W/K/cm^2$           |

| Photovoltaic: direct sunlight         | $10\mathrm{mW/cm}^2$          |

| Photovoltaic: indoor                  | $10 \mu\mathrm{W/cm}^2$       |

20 *Chapter 1.2*

with Moore's law. For the lowest bit rates, standby power (typically 50  $\mu$ W) is again a limiting factor.

Of course, a lot can be gained by proper system optimization. For example, microsystems can be provided with a "sleep mode", so that they consume power only intermittently, whereas energy scavenging is functional continuously. Yet, it can be concluded safely that with real smart dust type devices relying on energy scavenging or on a single non-replaceable battery, very limited computing and communication is possible. The realization of simple wireless sensor functions will undoubtedly be feasible, but ubiquitous computing and communication based on wireless and batteryless autonomous microdevices is likely to remain a dream.

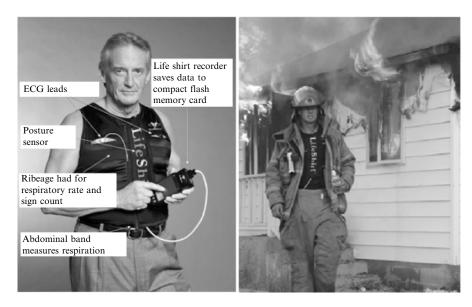

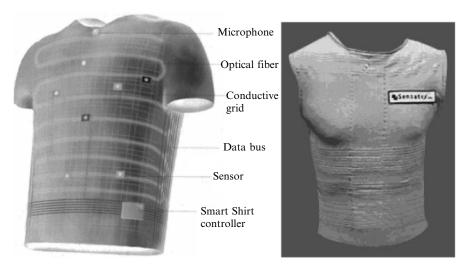

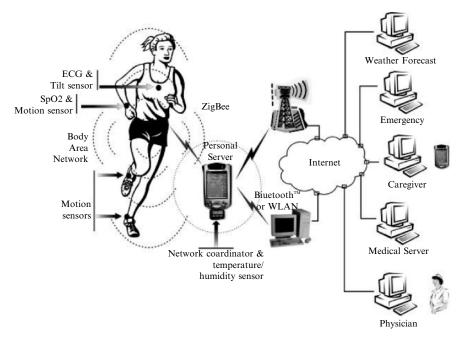

#### 4.4. Textile Electronics

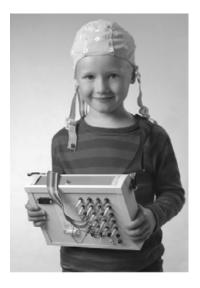

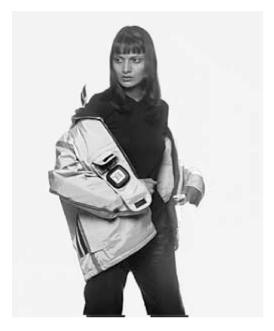

We are used to thinking of consumer electronics in terms of self-contained appliances, or "boxes." There are circumstances where such boxes are not the most convenient ways to package electronics. Think of a jogger carrying an MP3 player. It is not convenient to operate the tiny controls of such a device while jogging. Sportsmen, as well as elderly people, or individuals with an identified health risk may well want some of their body parameters to be monitored continuously. Examples are the electrocardiogram for sportsmen, or for heart patients, or the glucose concentration in the blood for diabetic patients.

Such cases call for electronics integrated into clothing. A first step could be to integrate controls and sensors in apparel. Systems researchers are already going a step further, and are investigating wireless "body area" sensor networks.

Device physicists and materials scientists need to come up with the enabling technologies for this new field of "textile electronics" [14]. What needs to be invented is soft controls, wiring and interconnect solutions, flexible segmented displays for signaling functions, and integrated sensors. One may also think of apparel woven from light emitting, or color changing fibers. By incorporating suitable fibers, also the textile itself can have sensorial functions, for example to measure the degree of stretch [15].

The application of textile electronics is not limited to personal apparel. Electronics can be incorporated in furniture, or soft furnishings (curtains and wall paper) as well. A research group working at Infineon has developed a concept for "intelligent carpets"[17]. These carpets are woven fabrics containing conducting wires, connecting and powering a two-dimensional array of (conventional silicon) chips. The chips form a self-organizing network: it can be cut into any shape, without losing its functionality. The carpet is provided with sensors, able to monitor

Figure 1.2-4. Textile photonics: LED's integrated into a pillow.

temperature, pressure, or vibrations. This approach may also be used to solve the energy supply problem of "smart dust" type of autonomous microdevices, allowing truly ubiquitous computing.

Energy scavenging looks like a viable option in the domain of wearable electronics. A human typically consumes 2500 kcal a day, or 10 MJ. This corresponds to an average power of about 100 W, which roughly equals the power consumption of a desktop computer. Starner [16] estimated that while walking about 5 W may be recoverable using appropriate transducers. This may be enough for wearable computing.

#### 4.5. Solid State Lighting

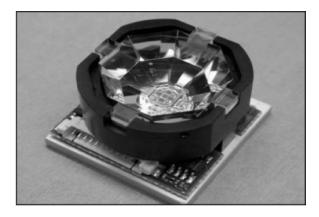

Light bulbs have provided the basic technology for the invention of electronics based on vacuum tubes. Yet, illumination as an application domain has remained relatively unaffected by electronics. Exceptions are electronic ballasts for compact fluorescent lamps, and electronic dimmers. However, we can expect that the emerging solid state lighting technologies based on light emitting diodes will change this state of affairs [18]. There are two major solid-state lighting technologies. The first is LEDs based on heteroepitaxial growth of III-V semiconductors that have shown an exponential increase in luminous efficacy, and they now offer very bright point sources. An LED lamp containing red, green, and blue LEDs can be controlled electronically to span a large part of the color triangle. In its most complex manifestation, one may expect that LED lamps of the future will encompass various LED dies, photo detectors and control electronics for active color control, passive or active microoptics for beam control, passive or active thermal management, and a wireless link.

22 *Chapter 1.2*

Such lamps will be made using SiP technologies. An early prototype is shown in Figure 1.2–5.

The second emerging solid state lighting technology is based on electro luminescent amorphous organic semiconductors, which can be deposited on large area substrates by evaporation (small molecules) or wet processing technology (polymers) — just as in the organic displays described above. Organic LED light sources will be ideal for large area diffusive light sources (see Figure 1.2–6). They can be flexible, and of any shape. They can be made to emit white light through the appropriate layer composition or red, green and blue pixels can be made in combination with some kind of a matrix-addressing scheme. It is also possible to make transparent light emitting devices on glass, enabling new applications, such as privacy or atmosphere providing windows.

It is expected that these LED technologies will show rapid growth in special lighting markets, followed by a penetration in the general lighting market. This will probably start with halogen lamp displacement. But eventually, one can envision a more dramatic impact. They may not require a socket because of the long lifetime of LEDs. In combination with the increased design freedom in tailoring the shape of organic LEDs, one can anticipate that entirely new types of luminaire will be designed.

Because of the added control over color and illumination intensity and distribution, the distinction between the lamp of the future and a display may become less sharp than we are used to. Perhaps the lamp of the future will be a flat light-emitting surface that shall also function as a touch screen, just like an interactive display. This way one could freely adapt parts of the surface that would emit light. The added degrees of freedom in

Figure 1.2–5. Color tunable solid state lamps will be based on System–in-Package technology.

Figure 1.2-6. An organic light emitting diode.

controlling the light output of solid-state lighting will also call for an increased number of (light) sensors and control functions in the environment. Digital control and wireless networks will play a role in this application domain as well. Solutions will eventually be found to provide lighting tailored to the specific mood of the people present. This will call for context awareness. Thus, the expected impact of solid-state lighting fits very naturally with the vision of AmI.

#### 5. MORE OF MOORE AND MORE THAN MOORE

#### 5.1. System on Chip and System in Package

Microelectronics has become the most pervasive global industry with products in almost any application domain, ranging from mobile communications, computing, and automotive electronics to personal healthcare, security and identification. Innovation in mainstream silicon microelectronics is following the path of Moore's law all the way down to the nanoelectronics size regime. In formulating his famous law, Gordon Moore not only made a lucid prediction but also provided a clear direction and time line for innovation in the semiconductor industry, which has enabled the definition of internationally agreed roadmaps. Because of this, the various actors in the industry ranging from materials suppliers to toolmakers, IC manufacturers, and software houses can be fairly confident that their expenditures on R&D are timely, well directed and profitable. On an architectural level, the winning solution is the SoC approach. Based on generic and standardized technology generations, a SoC

24 *Chapter 1.2*

provides a solution based on modular IP blocks, which can be designed using well-defined design rules with compact models describing the behavior of the individual devices. Because of its programmability, a SoC can be manufactured in large numbers for a range of applications, offering maximum reuse of costly design and testing effort.

Meanwhile, as described in this chapter, we are witnessing a diverse branching off of progress in microelectronics beyond the one-dimensional highway of Moore's law. Further miniaturization of electronics requires extensive integration of passive components, such as inductors and capacitors, which nowadays take up the majority of PCB area in, for example, a mobile phone. This requires new approaches in materials, design and processing as the traditional scaling rules for CMOS circuits do not apply here. Another trend is the increasing incorporation of a rich variety of novel functions into personal electronic systems. One may think of miniature camera modules, a personal weather station, GPS, accelerometers, biometric identification, and health monitoring systems. Apart from dedicated non-CMOS semiconductor process features, such as high-voltage, low power, analog, and radio frequency devices, non-semiconductor technologies too are needed to realize functions like integrated passives, or mechanical and optical sensors (MEMS). Nanotechnology and biotechnology are around the corner, and they will have a dramatic impact on this new class of sophisticated elements.

At an architectural level, the complexity can be addressed at least partially, by the concept of SiP. Where a SoC minimizes the cost per switch, a SiP focuses on achieving the highest value for a single packaged microsystem. Added value in a SiP is achieved by integration of several functions into a single module or package thereby combining electrical as well as nonelectrical elements. The challenge for SiP will be to develop a degree of standardization and reuse, so that an economically viable industry can be built. Of course, the economics will be quite different for high volume consumer applications and low volume professional applications, for example health care.

#### **5.2.** Open Innovation Approaches

In the world of "more of Moore", the exploding costs of realizing successive technology generations have become almost prohibitive. Dealing with the *soaring costs of innovation* is today the number one challenge for silicon microelectronics. The solution is offered by open innovation approaches [19]. As an early adopter of this approach, Philips Research has pioneered intensive partnerships in R&D. Thus, we are carrying out our advanced silicon process technology research together with the

Interuniversity Microelectronics Center (IMEC) in Leuven, Belgium. Philips semiconductors and its partners STMicroelectronics and Freescale carry out the subsequent development and pilot manufacturing in the Crolles 2 Alliance near Grenoble, France. By using advanced wafer foundries, such as TSMC of Taiwan, cost sharing and risk reduction is achieved in mass manufacturing as well.

The key challenge to be addressed in the new field of "More than Moore" is managing the *soaring complexity*, caused by the bewildering variety of applications and emerging technical solutions. Roadmaps are virtually nonexistent, and the pursuits of material suppliers, toolmakers, device makers, designers, and OEM customers are not yet well aligned. Added to this are the pitfalls of the innovator's dilemma: how to balance investments in a new application based on unproven technology against investing in the next generation of a predictable technology development?

In our view, the world of "More than Moore" can only become as successful as silicon microelectronics if we succeed also in this field in defining shared roadmaps, with attention for modular and platform solutions, common modeling, simulation and design tools, and shared testing strategies. This will call for intensive technology partnerships. Philips, being a strong believer in open innovation, is pursuing this actively by articulating and sharing our long-range application and technology visions with technology partners and key customers. We are also actively engaged in a variety of joint R&D programs with our technology partners.

As a concrete step toward open innovation in the new field of SiP, Philips Research has recently opened its new MiPlaza cleanroom at the High Tech Campus in Eindhoven, the Netherlands. Facility sharing is actively promoted here. Several third party start-up companies are already using MiPlaza today. Also, we are working together with toolmakers and with leading universities. It is our intention that MiPlaza will become a highly interdisciplinary meeting place for academic and industrial researchers in the field of microsystems and nanotechnology working together in a spirit of open innovation [20].

#### 6. CONCLUSION

Summarizing, we hope to have provided an idea about the type of physical layer challenges posed by vision of AmI. The major topics to work on are: ubiquitous, flexible and reflective displays, extreme miniaturization, and integration of new functions, such as sensors and actuators with silicon logic, textile electronics, and solid-state lighting technologies. A key bottleneck in the development of autonomous devices and

26 *Chapter 1.2*

ubiquitous computing is the energy supply of the distributed device nodes. Open innovation approaches will be required to manage the soaring complexity of this field.

#### **ACKNOWLEDGEMENT**

The author wishes to acknowledge the contributions of his colleagues at Philips, in particular Emile Aarts, Gerjan van de Walle, and Fred van Roosmalen.

#### **REFERENCES**

- [1] Emile A. and Stefano M., (eds), *The New Everyday, Views on Ambient Intelligence*, Koninklijke Philips Electronics N.V., 010 Publishers, Rotterdam (ISBN 90-6450-502-0).

- [2] Without claiming completeness: Sony is talking about augmented reality, IBM and MIT about pervasive computing, AT&T about sentient computing, Xerox about ubiquitous computing, Microsoft about intelligent environments, Georgia Institute of Technology about aware computing, and Stanford university about interactive workspaces.

- [3] Mark W., 1991, *The Computer for the Twenty-First Century*, Scientific American, pp. 94–110 September 1991. See also: Mark W., 1993, Some computer science problems in ubiquitous computing, *Communications of the ACM*, July 1993. (reprinted as *Ubiquitous Computing*, Nikkei Electronics, pp. 137–143.)

- [4] Hsu, V, J. M. Kahn and K. S. J. Pister, 1998, Wireless Communications for Smart Dust, Electronics Research Laboratory Technical Memorandum Number M98/2, February 1998.

- [5] Byron R. and Clifford N., 1998, *The Media Equation*, CSLI Lecture Notes, University of Chicago Press, Chicago.

- [6] Penterman, R., Klink, S., de Koning, H., Nisato, G., Broer, D., 2002, Nature, 417, 55.

- [7] Hayes, R. A. and Feenstra, B., 2003, Nature (London), 425, 383.

- [8] Estrin, D., Culler, D., Pister, K. and Sukhatme, G., 2002, Connecting the physical world with pervasive networks, *Pervasive Computing*, January 2002.

- [9] Kuiper, S. and Hendriks, B. H. W., 2004, Variable focus liquid lens for miniature cameras, *App. Phys. Lett.*, **85**, 1128.

- [10] Pistor, K., Schmidt, F., patent application WO 01/913115 A2. See also www.EnOcean.com.

- [11] West, W. C., Whitacre, J. F., White, V. and Ratnakumar, B. V., 2002, Fabrication and testing of all solid-state microscale lithium batteries for microspacecraft applications, *J. Micromech. Microeng.*, **12**, 58.

- [12] Roundy, S., Wright, P. K. and Rabaey J., 2003S A study of low level vibrations as a power source for wireless sensor nodes, *Computer Communications*, **26**(11), 1131–1144 July 2003.

- [13] Pelgrom, M., Roovers, R. and Bergveld H. J., *Smart Dust, in Ref.* 1 of Chapter 2.1. See also Bergveld, H. J., Kruijt, W. S. and Notten, P. H. L., 2002, *Battery Management Systems Design by Modelling*, Kluwer Academic Press.

- [14] Farrington, J., Moore, A. J., Tilbury, N., Church, J. and Biemond, P. D., Wearable Sensor Badge and Sensor Jacket for Context Awareness, J Farrington, AJ Moore, N Tilbury, J Church, PD... The Third International Symposium on Wearable Computers, 1999.

- [15] Gough, P., Wearable Technology, in Ref. 1 of Chapter 4.4.

- [16] Starner, T., 1996, Human powered wearable computing, IBM Syst. J., 35, 618.

- [17] Jung, S., Lauterbach, C., Strasser, M., Weber, W., *Enabling Technologies for Disappearing Electronics in Smart Textiles*, Solid-State Circuits conference, 2003. Digest of Technical Papers. ISSCC. 2003 IEEE International, 1, 386–387.

- [18] Zakauskas, A., Gaska, R., Shur, M., Shur, M. S., Zukauskas, A., 2002, *Introduction to Solid State Lighting*, John Wiley, New York.

- [19] Chesbrough, H., 2003, *Open Innovation, The New Imperative for Creating and Profiting from Technology*, Harvard Business Press, Boston.

- [20] Information about the MiPlaza cleanroom can be found at http://www.research.philips.com/institutes/index.html.

## Section 2

**Wireless Communication**

## CIRCUITS AND TECHNOLOGIES FOR WIRELESS SENSOR NETWORKS

#### Brian Otis

Electrical Engineering Department University of Washington, Seattle, Washington botis@ee.washington.edu

Mike Sheets, Yuen-Hui Chee, Huifang Qin, Nathan Pletcher, and Jan Rabaey Berkeley Wireless Research Center, University of California, Berkeley jan@eecs.berkeley.edu

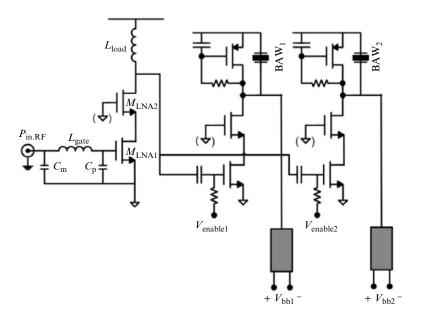

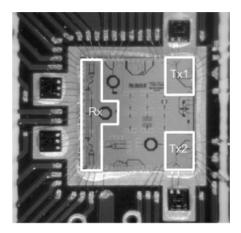

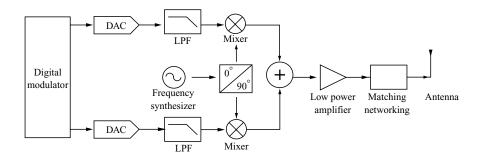

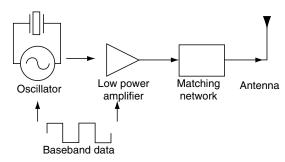

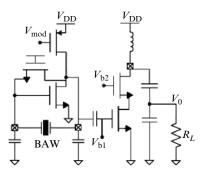

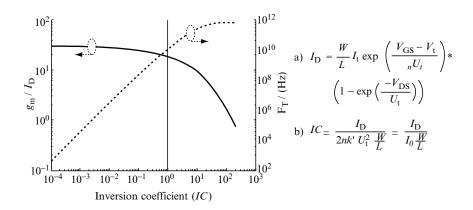

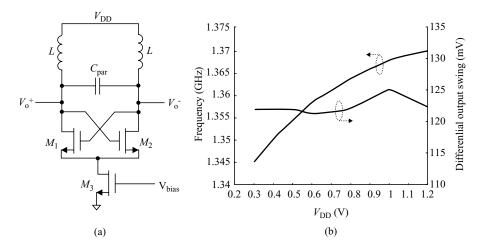

Abstract Successful deployment of wireless sensor and actuator networks in sufficient numbers to provide true ambient intelligence requires the confluence of several disciplines including networking, low power RF and digital IC design, MEMS techniques, energy scavenging, and packaging. Progress in each of these areas has been documented and proof-of-concept prototypes have been tested. Research in RF transceiver design utilizing bulk acoustic wave resonators has yielded fully integrated, ultralow power transceivers. Novel digital circuit design techniques, including aggressive power management, robust subthreshold logic operation, and ultralow voltage SRAM with data retention enable efficient computation. These technological advances should be accompanied by novel opportunistic networking and media access techniques to provide robustness and decrease the duty cycle of the node. Future challenges include the integration of a sub-50  $\mu$ W carrier sense detector for asynchronous and non-beaconed receiver wake-up, efficient hybrid energy scavenging power generation, and cheap, robust three-dimensional packaging techniques.

Keywords leakage reduction; MEMS; RF CMOS; SRAM

#### 1. INTRODUCTION

The successful large-scale deployment of wireless sensor networks (WSN) will yield large benefits for environmental, medical, and security

monitoring applications [1]. A truly ubiquitous deployment is economically feasible only when the cost and size of the individual elements become negligible. Achieving such a diminutive stature requires a minimal number of components, favoring those that are inexpensive, have a high level of integration, and have simple packaging and assembly requirements. In addition, the cost of deployment and maintenance of the network should be negligible. The physical implementation of an individual network node is constrained by three important metrics: power, cost, and size. These requirements are outlined below.

- Power: To reduce installation cost and to allow flexible deployment, most nodes must be untethered and have their own energy source. Frequent replacement of the energy source is infeasible because it would result in a high maintenance cost. Thus, the nodes must scavenge their energy from the environment. This requires the average power dissipation of the node to be extremely low  $(< 100 \,\mu\text{W})$ .

- Low Cost Implementation: For commercial viability, the cost/area of the wireless sensor network mesh must be very small. For network reliability, the node density (nodes/area) must be high. Thus, the cost of each node must be extremely small (<\$1US).

- Small Form-Factor: Embedding the components into the infrastructure of daily life (walls, furniture, lighting, etc.) requires a small form factor for each node. For many scenarios, sizes smaller than 1 cm<sup>3</sup> are necessary. A very high level of integration is mandatory if such small dimensions are to be achieved.

This chapter discusses circuits and technologies aimed at realizing the ubiquitous deployment of WSNs. We begin with an exploration of advancements in digital computation that reduce active and standby power requirements. Recent and future research in RF communications links is then described.

#### 2. EFFICIENT DIGITAL COMPUTATION

As process dimensions and supply voltages decrease, the CMOS leakage power becomes a significant component of the total power budget. This is particularly true for sensor nodes because the low duty cycle means that a large portion of the total time is spent idling. This section describes techniques to reduce the leakage power consumption of the digital computational blocks and embedded memory.

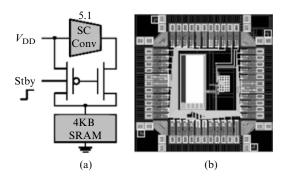

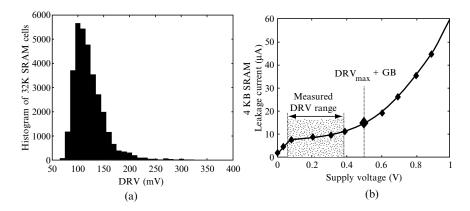

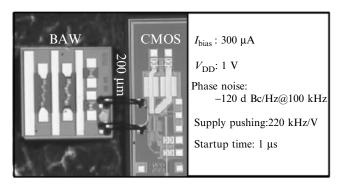

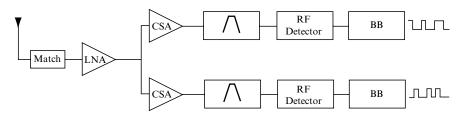

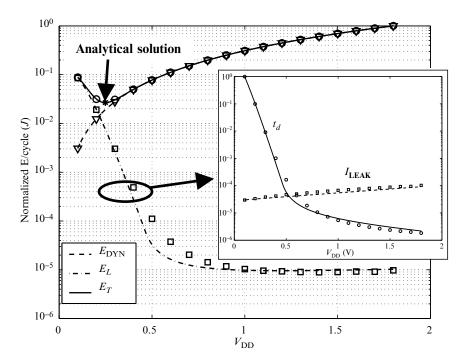

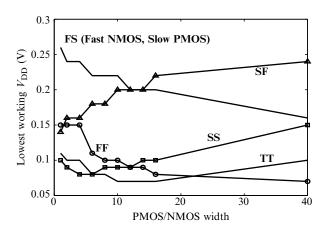

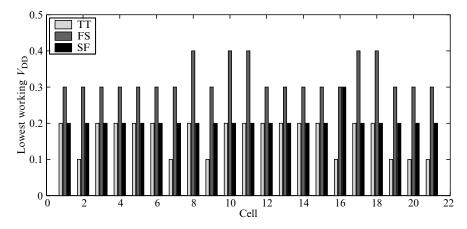

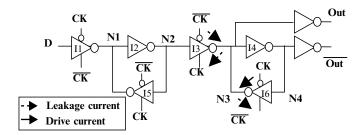

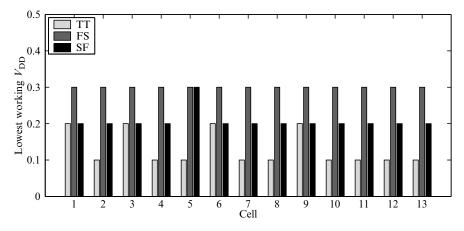

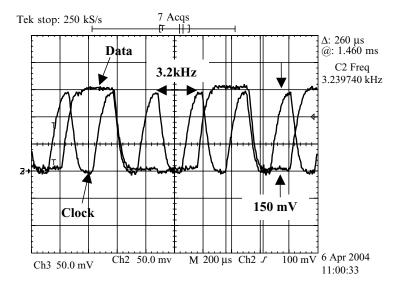

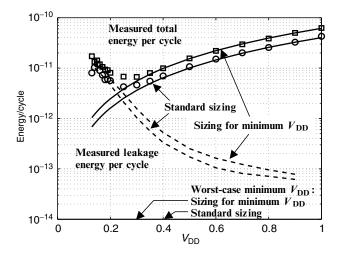

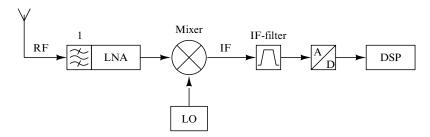

#### 2.1 Advanced Power Management